从底层重新认识D触发器、建立时间和保持时间

从底层重新认识D触发器、建立时间和保持时间

时间: 2024-02-08 17:28:31 | 作者: 半岛官网入口

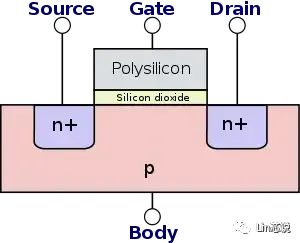

)或 IGFET(绝缘栅场效应晶体管)是一种场效应晶体管,它在栅极和主体之间利用绝缘体(如 Si

详细介绍

)或 IGFET(绝缘栅场效应晶体管)是一种场效应晶体管,它在栅极和主体之间利用绝缘体(如 SiO2)。如今,MOSFET 是数字和

NMOS和PMOS 的区别体现在其衬底和掺杂类型的不同,NMOS 的衬底为P型半导体,掺杂两个高浓度的 N 型半导体,并用铝金属引出两个电极分别为作为源极(Source)和漏极(Drain),并在半导体表面覆盖一层很薄的 SiO2 作为绝缘层,在源极和漏极之间的绝缘层上添加一个多晶硅(Polysilicone)作为栅极(Gate),最后在衬底引出电极,这样就构成了 N 沟道增强型 MOS 管。

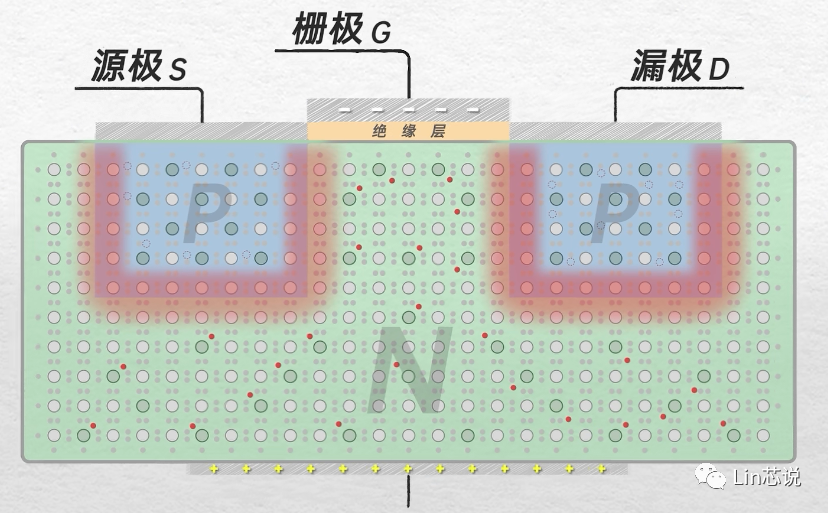

PMOS 和 NMOS 大体相同,在衬底变成 N 型半导体,在掺杂的为 P 型半导体,其余和 NMOS 如出一辙,但是仅仅就是这两点区别,却使得它们的特性完全不同。

对于 NMOS 管,当对栅极进行正向偏压(高于阈值电压)时,在绝缘层下方就会汇集大量的电子,由于 N 型半导体多电子,就会与两侧的 N 型半导体形成 N 沟道,进而实现整个回路的导通,如果施加的电压低于阈值电压,则没办法实现导通。

同样的对于 PMOS 管,由于衬底和掺杂物互换,如果施加的电压高于阈值电压,在绝缘层下方就会汇集大量空穴,在两个 P 型半导体之间就会形成阻隔,无法导通。如果施加电压低于阈值电压,则可以导通。

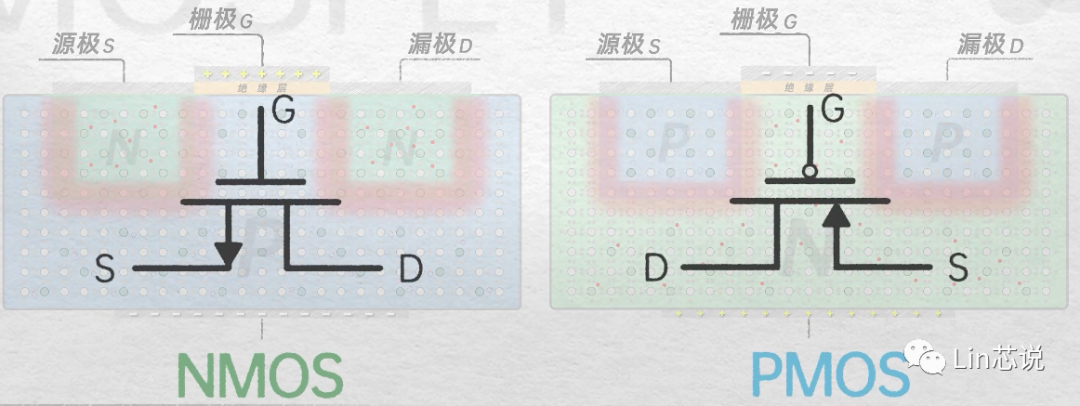

NMOS 和 PMOS 在专业电路图如下所示,NMOS 由栅极指向源极,PMOS 由源极指向栅极,并且 PMOS 在栅极处有取反标识。

NMOS 的特性:Vgs 大于一定的值就会导通,适合用于源极接地时的情况(低端驱动),只要栅极电压达到阈值电压就可以了。

PMOS 的特性:Vgs 小于一定的值就会导通,适合用于源极接 VCC 时的情况(高端驱动)。但是,虽然 PMOS 可以很方便地用作高端驱动,但由于导通电阻大,价格贵,替换种类少等原因,在高端驱动中,通常还是用 NMOS。

因为 PMOS 管是空穴导电,NMOS 管是电子导电,而电子的迁移率约是空穴的 2 倍,因此PMOS 管要宽一些增加迁移速率。

将 PMOS 与 NMOS 的漏极和栅极相连,给 PMOS 的源极接 VDD,给 NMOS 的源极接 GND,给两个的共同栅极 In 输入高于阈值电压,在前面介绍过,此时 PMOS 截止,NMOS 导通,所以输出 Out 相当于接 GND 拉低,而输入 In 低于阈值电压时,此时 PMOS 导通,NMOS 截止,所以输出 Out 相当于接 VDD 拉高。

可以发现就是反相器,这是最经典的 CMOS 结构,需要消耗 2 个晶体管搭建。

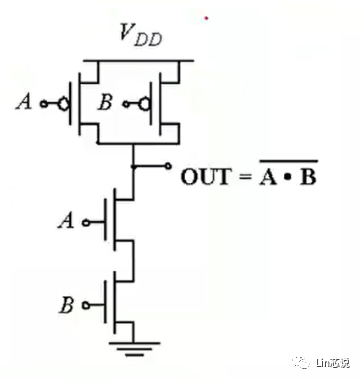

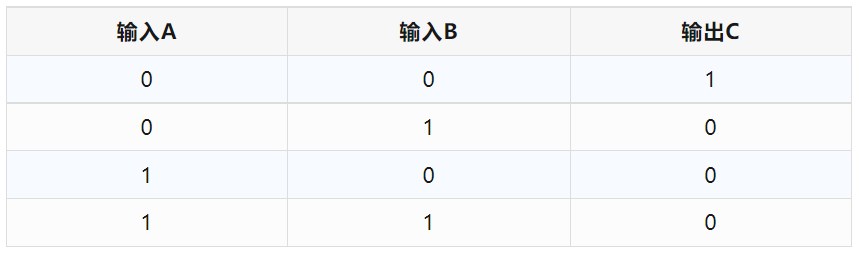

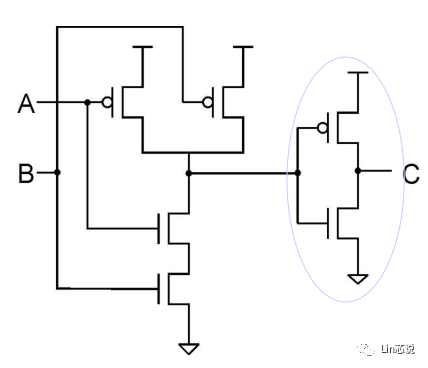

从与非门的真值表中能够准确的看出,只有输入 A 和 B 都为 1 的情况下,输出才为 0,其他情况输出均为 1,结合到 PMOS 和 NMOS 的性质来看,对于输出为 0 的情况,NMOS 输入为 1 则导通也就是接地为 0,并且要输入同时为 1,相当于把两个 NMOS 串联,而对于输出为 1 的情况,只要两个输入其中有一个为 0 则输出为 1,因此相当于把两个 PMOS 并联,于是得到了以下的逻辑门电路。搭建与非门逻辑门需要耗费 4 个晶体管。

有了上面与非门的铺垫,或非门就更好理解了,由真值表可知,只有在输入都为 0 的情况下输出为 1,只要输入有 1 则输出为 0,和与非门恰好相反,需要将 PMOS 串联接在上端,NMOS 并联接在下端,便得到了或非门的逻辑门电路。同样需要消耗 4 个晶体管。

与门就是在与非门的基础上,在输出端接上一个非门即可。不难发现搭建与门电路需要消耗 6 个晶体管,在一些文章或书籍中看到说在设计中使用与非门比与门更节省资源,实际上的意思就是这个原因。

同理或门也是一样,这里就不一一列举了,或门所需要的晶体管同样为 6 个。

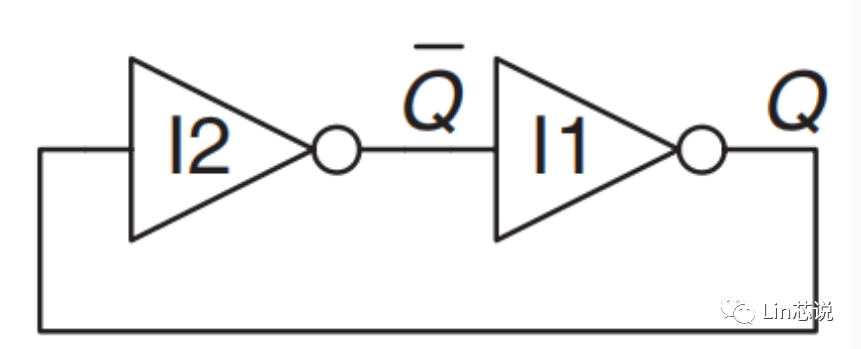

这种结构较为简单,当输入为 1 时,经过两级反向器输出仍为 1,输出又作为输入。

在对称结构中,Q 的输出作为 Q 的输入,同样 Q 的输出作为 Q 的输入。这里先假设 I1 的输入为 1,经过反相器输出得到 Q 为 0,同时作为 I2 的输入为 0, Q 的输出为 1。这样输出就能稳定为 1。反过来假设 I1 的输入为 0,经过反相器输出得到 Q 为 1,同时作为 I2 的输入为 1, Q 的输出为 0。这样输出就能稳定为 0。Q 和 Q 互为对方的输入,构成双稳态结构。

这种双稳态结构虽然结构相对比较简单,但是缺点在于无法控制其最终的输出,并且在结构上是没有输入的。

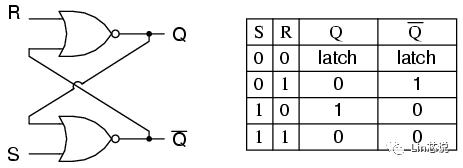

在上面的双稳态结构中形成的是闭合的回路,无法给到输入,这样的结构是无法保存数据的,因此就有了下面的结构,带有两输入的 SR 锁存器结构,主体由两个或非门构成,设上下的或非门为 N1、N2。

R 端输入为 1,N1 的输出 Q 为 0,而 Q 又作为 N2 的输入,Q 为 1,此时表示 R(Reset,复位)有效,Q 输出恒为 0。

S 端输入为 1,N2 的输出 Q 为 0,而 Q 又作为 N1 的输入,Q 为 1,此时表示 S(Set,置位)有效,Q 输出恒为 1。

R 端和 S 端输入为 0,假设 N1 的输出 Q 为 0,而 Q 又作为 N2 的输入,Q 为 1,Q 又作为 N1 的输入,得到 N1 的输出仍然为 0。假设 N1 的输出 Q 为 1,而 Q 又作为 N2 的输入,Q 为 0,Q 又作为 N1 的输入,得到 N1 的输出仍然为 1。此时表示 R(Reset,复位)和 S(Set,置位)都无效,输出保持输入不变(hold),也即是常说的产生 latch,把数据给锁存起来了。

在这个条件下是无意义的,此时 Q 和 Q 都为 0,显然是不对的,不能同时复位和置位。

对比前面的双稳态结构,SR 锁存器就有了锁存数据的功能,即当 S 和 R 都为 0 时,输出会从始至终保持原有的输入值不变。

RS 锁存器虽能锁存数据,但是当 S 和 R 同时为 0 时结果会出错,对使用带来不必要的麻烦,因此就需要去规避,所以有了 D 锁存器。

D 锁存器在 RS 锁存器的基础上增加了一些控制,E 可以看做使能信号,一般也可以为时钟Clk 信号,基于此对此电路结构可以进行分析。

E = 0,则对应 R、S 输入都为 0,参照 RS 锁存器的真值表得到此时为 latch,可以锁存数据。

E = 1 且 D = 0,此时上面的与门由于 D 取反为 1,与门输出为 1,相反的,下面的与门输出为 0,对应 RS 锁存器为 R = 1、S = 0,对应 Q 为 0。

E = 1 且 D = 1,此时上面的与门由于 D 取反为 0,与门输出为 0,相反的,下面的与门输出为 1,对应 RS 锁存器为 R = 0、S = 1,对应 Q 为 1。

对上面的结果进一步分析,不难发现 Q 值和 E 值息息相关,当 E = 1 时,此时 Q 输出为 D 的值,当 E = 0 时,此时数据被锁存。这样做才能够发现 D 锁存器是电平敏感的器件,控制信号 E 一般为时钟信号,并且这个例子的 D 锁存器为高电平敏感的。

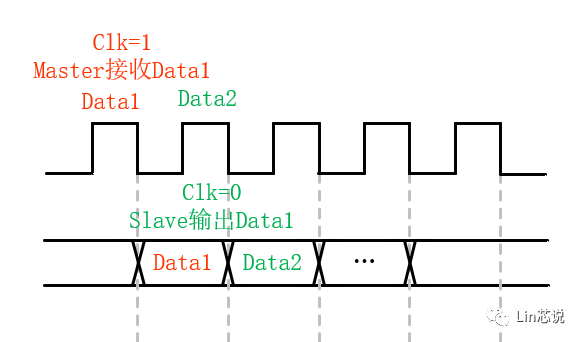

D 触发器实际上的意思就是将两个 RS 锁存器串联起来,第一个 RS 锁存器称为 Master,第二个 RS 锁存器称为 Slave,Master 的输出作为 Slave 的输入,但是两个 RS 锁存器的时钟使能输入恰为相反。

就这样循环往复的运作,能够准确的看出这个例子的 D 触发器是下降沿有效的,也就是在时钟下降沿到来时,将输出数据,其他时候数据保持不变。如果是上升沿有效的,只需要将反相器接在 Master 上。

当时只知道触发器要建立时间和保持时间使得工作稳定,但是为什么要建立时间和保持时间呢?秉持着对知识点刨根问底的态度,这里就从更底层出发,去深究触发器为什么要建立时间和保持时间。

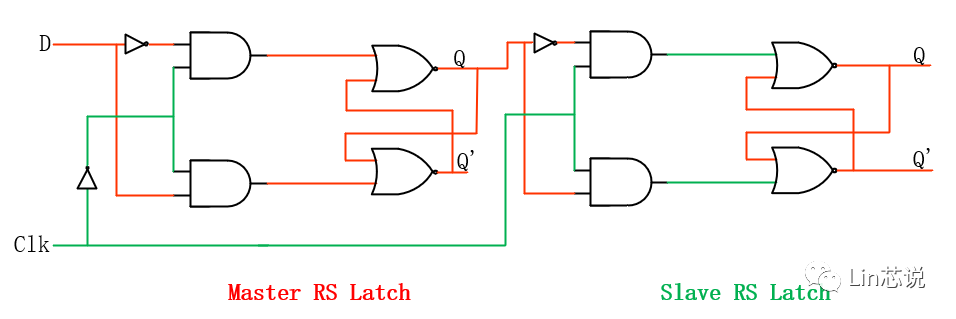

下图就是 D 触发器的内部结构展开图,其主要有两个 RS 锁存器组成,在前面的为 Master,后面的为 Slave,两个锁存器串联共用一个时钟信号,但是两者极性相反,为了更符合习惯,这里的触发器定为上升沿敏感的。

在前面分析过,在数据传输时,Master RS 锁存器负责将数据锁存,Slave RS 锁存器负责将 Master稳定锁存的数据输出。因此输入在从 Master 输入到 Slave 输出是一个顺序执行的过程,也就是说要想从 Slave 顺利输出数据,那么在 Master 就必须顺利锁存好数据。

那就先看 Master RS 锁存器是如何对输入数据来进行锁存的,数据的路径如下图中的红线所示,当时钟 Clk 为 0 时,数据从 D 输入(假设数据输入为 0)经过反相器历时 t1,数据变成 1,经过与门历时 t2 数据变成 1,再经过或非门历时 t3,由于此时数据为 1,所以经过或非门 Q 端输出为 0,Q 端输出又作为下面的或非门输出为 1,并且在此历时 t4,最终在 Q 端输出 0,此时数据便顺利被锁存起来。

这里忽略不计门与门之间的路径延时时间,只对时间做个大概分析,从这里可以计算得到所历经的总时长为:t1+t2+2*t3+t4,这一段时间就可以大致认为是触发器的建立时间 Tsetup。当经过 Tsetup 后数据被稳定的锁存,当时钟上升沿到来时(0->

1),Slave RS 锁存器就可接受到正确的数据并输出,如果不满足建立时间需求的话会发生啥情况呢?

假设此时不满足建立时间需求,当需要被锁存的数据在还未进入到第一个或非门时,时钟上升沿就已经来到,此时 Q 端输出的数据仍然是上一次被锁存的不确定数据,可能为 1 也可能为 0,这样 Slave 输出的数据就可能会出错。

再来分析一下保持时间,如下图中绿线为时钟到达与门的路径延时假设为 t5,蓝线为数据到达与门的路径延时假设为 t6,因为时钟路径存在反相器延时,所以延时会大一些,即 t5>

t6,假设在 Slave 输出数据的过程中,输入数据 D 由原来的 0 跳变到 1,此时由于 t5>

t6,就非常有可能使得与门的两个输入同时为 1(时钟上升沿来临之前 Clk 为 0,经反相器输出为 1),此时与门输出为 1,推出 Q 输出为 0,进而 Q 输出为 1,于是新到来的输出 Q = 1 就会将影响原来的 0,最后导致锁存的数据为 1,最终 Slave 的输出为 1,导致数据出错,这就是为什么输入数据需要在时钟上升沿来临之后仍就保持一段时间(t5-t6)不变。

从上面的分析能得出,D 触发器的建立时间要求比保持时间要求要更严苛,这也是在 RTL 设计综合后,建立时间违例比保持时间违例更频繁的原因,要求高了自然就更难达到,同时建立时间和保持时间也是相悖的,建立时间要求数据路径延时更小,数据路径延时越小,Master 锁存器更容易将数据锁存;保持时间希望数据路径延时更大,一旦使得数据路径延时 t6>

t5,Slave 锁存器输出的数据就不会出错。

次阅读 --

次阅读 --

次阅读 --

物理含义 /

有要求吗?刚看到一个门控时钟产生毛刺的反例,(如下图)想到了这样的一个问题。若此时钟信号毛刺极小,有没有可能被

次阅读 --

次阅读 --

次阅读 --

都是针对的时钟沿,如图所示,时钟沿有一个上升的过程,图中虚线与clk上升沿的交点是什么?幅值的50%?还是低电平(低于2.5V)往高电平(高于2.5V)跳转的那个点?

次阅读 --

次阅读 --

次阅读 --

次阅读 --

次阅读 --

次阅读 --

可以说是出现频率最高的几个词之一了,人们对其定义已经耳熟能详,对涉及其的计算(比如检查时序是不是正确,计算最大频率等)网上也有很多。

次阅读 --

? /

是SOC设计中的两个重要概念。它们都与时序分析有关,是确保芯片正常工作的关键因素。

次阅读 --

次阅读 --

裕量 /

【国产FPGA+OMAPL138开发板体验】(原创)4.FPGA的GPMC通信(ARM)EDMA

【先楫HPM5361EVK开发板试用体验】(原创)5.手把手实战AI机械臂

全国大学生计算机系统能力大赛操作系统设计赛-LoongArch 赛道广东龙芯2K1000LA 平台资料分享

- 上一篇:DC-DC电源电路

- 下一篇:最全面的霍尔传感器介绍以及六种典型电路剖析

返回