时序逻辑电路规划之D触发器

详细介绍

脉冲到来时间从一个状况翻转到另一个状况,其具有的存储特性也是时序逻辑的基本特征。

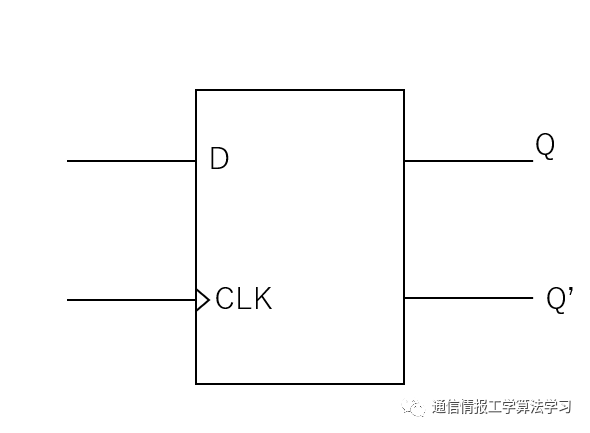

将其绘制成一个模型,最简略的如下图表明,D为数据输入端,clk为时钟输入端,Q为数据输出端口。

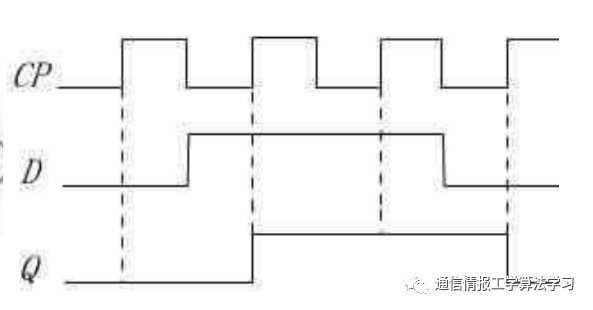

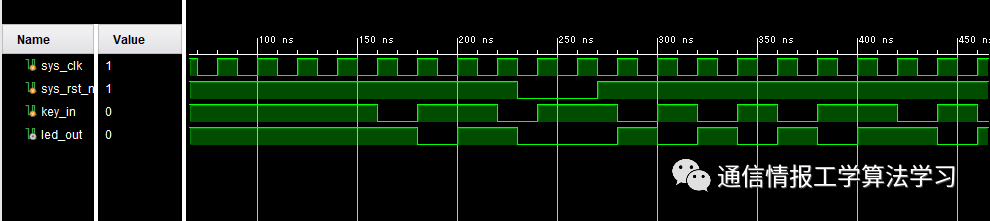

这种D触发器的功用也是适当简略的,便是当CLK上升沿到来时,Q的输出等于D,特征方程写为Q=D* (没有一点操控输入的情况下)。 波形图如下所示:

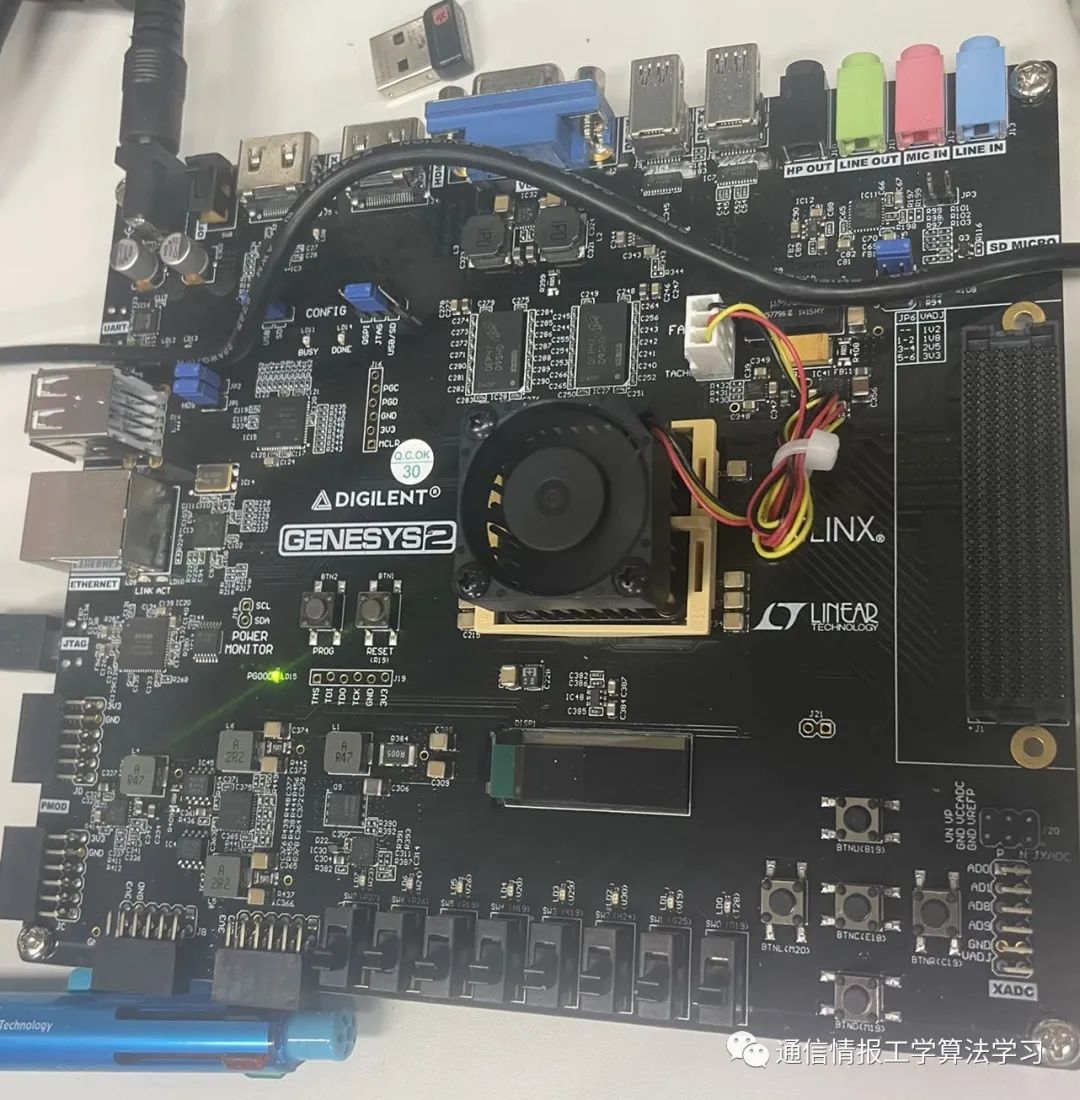

为了进一步详细得知其作用,接下来在FPGA开发板上展现其功用,运用的办卡为德致伦的genesys2,芯片为kintex-7系列的xc7k325tffg900-2。

为了愈加全面一些,在此为D触发器添加复位功用(按下按钮回到初始状况),此刻可以有两种复位D触发器,一种是同步复位,一种是异步复位。

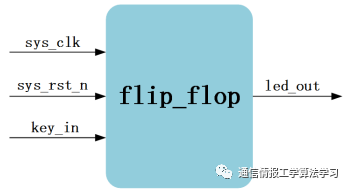

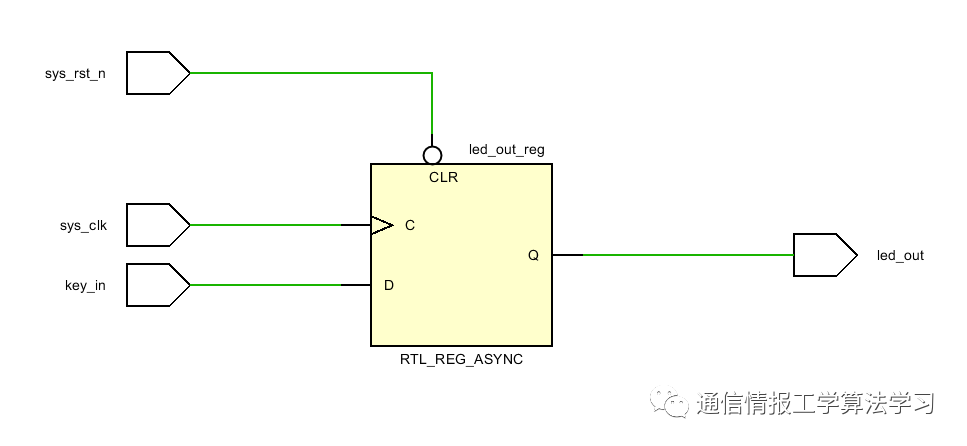

阐明一下各个端口的作用,sys_clk为时钟,sys_rst_n为复位,key_in为按键输入,即为触发器的D,led_out为输出,本demo会将其接到开发板的灯上,用灯的亮灭展现D触发器的作用。

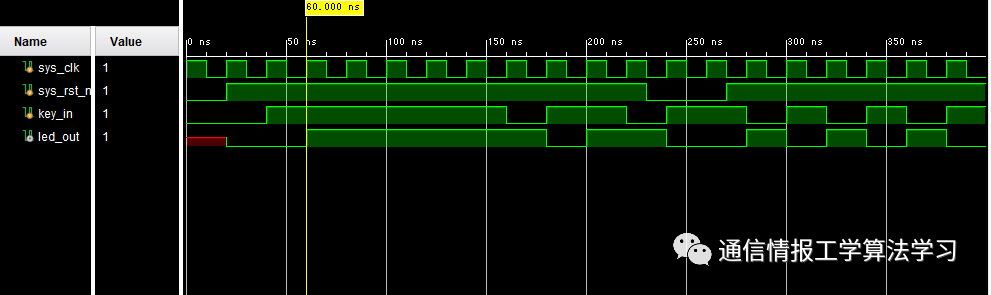

首要展现同步D触发器的verilog代码和testbench以及仿真成果。

可以发现,虽然体系现已处于复位开释的状况(复位键为高电平),时钟,数据和上升沿也都到来,可是输出会在时钟的下一拍进行改动。 **即:当时钟和信号在同一时间改动时,咱们以时钟的上升沿前一时间收集的输入信号为根据来发生输出信号。 **

下面是异步D触发器的代码,区别是添加了复位下降沿到来时间的敏感性(always句子),testbench和同步D触发器的共同。

可以观察到复位下降沿到来时间,输出立刻置为0,通过归纳之后的RTL电路如图所示,和规划(异步D触发器电路,同步D触发器电路多一个MUX模块)的差不多。

此次试验中呈现的一个问题是,此次运用的FPGA现已没有单端口时钟输出,所以要调用PLL的IP核组成输出一个单端口的时钟信号,这个预备下一篇再说。

的规划) /

的办法通常是比较相邻的两种状况(即现态和次态)。 例 1:列出下表所示

的剖析办法 /

全志R128 SDK HAL 模块开发攻略——Flash Controller

用74192规划倒计时电路,proteus仿真时为什么手动改动逆计数的时钟引脚时可以直接进行计数

- 上一篇:D触发器与Latch锁存器电路规划

- 下一篇:PCB设计

返回